DIY-Calculator Hardware:Community Portal

From DIY-Calculator_Hardware

The DIY Calculator Hardware Project consists of several sub projects:

- Creating the real hardware: a printed circuit board (PCB) with the processing chips, an LCD module, switches, and connectivity to a host computer

- Implementing the DIY Calculator CPU together with supporting functional blocks within a programmable logic chip (a so-called "Field Programmable Gate Array" - FPGA).

- Writing the firmware running on the hardware, including a ROM monitor

- Adding a software tool for communicating with the hardware (e.g. uploading user programs)

On this page you will find information about the progress of the project as well as technical details.

Contents |

Hardware Project

The layout will somewhat resemble the layout of the (virtual) DIY Calculator with an 20x1 character LC display and a 70 keys sensor key matrix. Additionally there are connectivity means for a host PC:

- Serial (RS-232) for uploading user programs and providing a console to the DIY Calculator CPU

- A JTAG programming connector; this connects to the PC's parallel port and enables the user to load new designs into the FPGA

- Additionally there will be sockets for external ROM/RAM chips and a large prototyping area for free use.

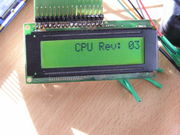

Project status (9.Oct.2006): New LCD module tested and integrated. The original planned 20x1 LCD module is hard to get, so we evaluated additionally 20x2 types (this mainly has impact on the mechanical hardware design).

Project status (31.Aug.2006): Test of sensor keypad was successful. Here are the photos:

Project status (13.Aug.2006): Prototype PCB layout completed. Here are the "final" schematics:

keypad mechanics:

and the layout:

Test of sensor keypad is in progress.

Project status (7.Aug.2006): We decided to separate the functionality into two PCBs: the FPGA with surrounding components and the sensor keypad. This gives even more flexibility for different I/O modules. Here are the updated schematics:

Project status (19.Jul.2006): schematics completed, PCB layout work started

- Schematics preliminary

FPGA Project

The PCB will contain an FPGA chip in the 10K-gates size-class (Lattice LFEC10E-3F256C) with a 256 pin BGA footprint. The included JTAG connector makes this a development board for general use. With ispLEVER, the FPGA development software suite from Lattice Semiconductor, the FPGA design can be altered or a completely new design can be made. The entry level version of ispLEVER (ispLEVER-Starter) can be downloaded freely from Lattice. With Lattice's ispVM System the design can be transferred via JTAG to the DIY Calculator PCB.

The FPGA design of the DIY Calculator is based on the work of Steven Cooper, Carl Hoggins, Bjornar Prestegard, Svein Roar Kvaale, and Dr Albert Koelmans (instructor) of the University of Newcastle Upon Tyne, England.

Additionally to the CPU and ROM and RAM there will be special logic for the switch matrix, for LCD output, and a UART for RS-232 communication to the host PC.

Project status (19.Jul.2006): concept proved, integration of the existing VHDL design (was done with Altera/Quartus) into ispLEVER

Project status (7.Aug.2006): Simulation of the existing CPU design revealed big troubles. A new design of the CPU is being made.

Project status (31.Aug.2006): new CPU design is ready! (simulated and tested in a Lattice FPGA development board.)

Download the VHDL code from here: DIY-Calculator_Hardware:Downloads

Next steps are design/integration of:

- LCD controller

- UART

- Keypad controller

- stay tuned!

Notice that there are two access cycles to the LCD module with each character, one which actually writes the character and a second one which shifts the display left, resembling the display behaviour of desktop calculators.

Also note that during LCD accesses the CPU is effectively halted by the nWAIT signal which is generated by the LCD controller. Between LCD accesses there is activity on the CPU data and address bus, which indicates the loading of the next character, etc. View the "Hello World" program here: hello-tasm.lst

Note the "tx_empty" signal which denotes an empty transmitter register. During the shifting-out of the character tx_empty goes low thereby indicating that the CPU must not write a next character. The CPU is busy during this phase with polling the UART status register waiting for tx_empty going high again. tx_empty may trigger an interrupt request, if enabled by software.

Line speed is 38.4 kbaud.

Here the "rx_ready" is signal used for CPU handshake. When a character ('U' / $55 in the picture) is received rx_ready becomes high thus indicating to the CPU that a character is available n the UART for reading. When the CPU reads the character rx_ready goes low again. In the screen shot the CPU writes then the character to the LCD, which is easy recognizable as the CPU is halted during LCD access by means of the "nWAIT" signal. View the program listing here: uart-test.lst

Line speed is (as with transmit) 38.4 kbaud.

Two key presses are simulated: first key '5' and then key '9'. See the scan rows changing (e.g. row1, row1_last) detecting changes and generating the 'key_set' signal which latches the respective key code. This in turn causes the KEYPAD input port to change from $FF to the key code ('d_out' signal). When the CPU reads from KEYPAD (short pulse on 'sel' line) a pulse on 'beep' signal is generated and the KEYPAD port value is reset to $FF. Note the (with the first key press) the '5'-key is still depressed when the CPU reads the KEYPAD but no additional key events are generated. In the second case ('9'-key) the key is released before the CPU reads KEYPAD.

Project status (9.Oct.2006): Added a controller module for SPI flash ROM (FPGA configuration ROM) access (see controller state diagram):

At cursor 'A' the command ($AB) is issued to the flash controller, afterwards the command plus 3 dummy bytes (as per flash data sheet) are transmitted to the flash via the SPI interface. During this time the CPU waits for the response. At cursor 'B' the CPU detects that a new data byte from the flash is ready (reading $06 from the status port). At cursor 'C' the response is read ($13 for the used M25P80 chip).

ROM Monitor Project

On of the primary goals of the DIY Calculator project is to teach how computers are working on machine language level ("How Computers Do Math"). So everyone is highly encouraged to translate various algorithms into assembly programs for the DIY Calculator. The current virtual DIY Calculator comes with a ready-to-use environment, which includes the calculator-like user interface, an assembler, a simulator, single-step debugger, and memory and register display. When translating the design to a physical one there has to be an environment, too. The most important functionality (and this is the only one being in scope of this project) is to run user programs to the DIY Calculator hardware. To be able to do that there must be means of:

- uploading the program to the hardware

- store it in some non-volatile storage

- actually run it

- obtain some status information (e.g. terminated correctly, does not fit into memory, etc.)

This is the objective of the ROM monitor. The ROM monitor is, as its name suggests, a program which resides within the ROM of the DIY Calculator. It is always present there and provides for the above mentioned supervising tasks. It uses the RS-232 port both for transferring the user program and as console port to which you can connect with a terminal emulation program (or a real "dumb" terminal if can get hold of one ..) to enter commands and display status information. The ROM monitor will be written in the DIY Calculator's assembly language and will additionally supply some basic functions (e.g. status/log output via RS-232) to user programs.

Project status (19.Jul.2006): basic conceptual design ready

Project status (7.Aug.2006): no changes

Project status (31.Aug.2006): no changes

Project status (6.Sep.2006): work started

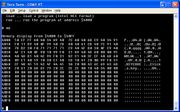

Project status (12.Sep.2006): First time that a program has been loaded and run to the DIY Calculator successfully! See terminal screen shot:

I loaded this program: keycode.lst, which waits for a key press and then displays the key code. Download the .ram file (keycode.ram) and load it into your virtual DIY Calculator. In the real world you press buttons on the PCB and the codes are displayed on the LCD:

Project status (13.Sep.2006): support of the DIY Calculator native hex format (.ram files).

Project status (15.Sep.2006): working on interrupt code - stay tuned!

Project status (19.Sep.2006): UART Rx interrupt now works reliable. First steps with Single-Step interrupt are promising - see screen shot:

Project status (22.Sep.2006): Single-Step and Run buttons work! Clive (Maxfield) contributed the assembler code for it and after finding a basic obscurity inside the interrupt structure it worked out of the box with only a few minor flaws. Thank you, Max!

Thanks to that it is now possible to load a program and single-step debug it on the real hardware!

See the program listing and the terminal log (with remarks): simpled.lst simpled-debug.txt

To end a debug session press either 'Run' to run the program or you press 'Reset' for a hard reset or you press 'CTRL-C' on the terminal for a soft reset.

Project status (9.Oct.2006): Added access to the configuration flash ROM of the FPGA (see FPGA part). There are three new commands for managing the flash:

- 'cpflash [address] [# of bytes]': copies # bytes from RAM to flash, starting ad address

- 'cpram [address] [# of bytes]': copies # bytes from flash to RAM, starting at address

- 'eflash': erases the flash

More information on flash usage: The FPGA is based on a volatile storage technology (SRAM cells). Thus it has to be loaded (or configured) each time power is applied. This can be done using several different mechanisms, one of the easiest is using a serial (flash) PROM which contents is automatically loaded into the FPGA by some hard-wired logic inside the FPGA after power-on. The amount of memory needed inside the flash ROM is determined by the size of the FPGA. The FPGA chip we use on the DIY Calculator is a Lattice LFEC10E chip requiring about 3.1Mbit storage. It depends on the used flash memory how much free space remains. The free space can be used to store user data. The memory inside the flash is sectorized with 64KB each sector. We use the topmost sector for storing the user program that is intended to run on the DIY Calculator. During a hard reset all RAM is restored from flash. When erasing the flash only the topmost sector is erased, keeping FPGA configuration information. Likewise, when writing to the flash the sector address is fixing thus preventing overwriting vital FPGA config data.

Upload Utility Project

The user program upload process is handled by the ROM monitor on the DIY Calculator side. But there must be a means of sending a program to the DIY Calculator. While it is possible to send a file with the terminal emulation program a GUI program is preferable. Furthermore, by having a dedicated program for this task it is possible to generate a check sum or use a protocol of choice for ensuring correct transmission. The transmission status (success/failure) can be displayed. This program should be written in "C" using the GTK library of GUI widgets to be easily ported to different platforms.

Project status (19.Jul.2006): considered

Project status (7.Aug.2006): no changes

Project status (31.Aug.2006): no changes